摘要:介紹了IEEE 1394h串行總線" title="串行總線">串行總線的特點,并以FPGA" title="FPGA">FPGA嵌入式處理器Nios II" title="Nios II">Nios II為控制核心,設計實現了一種1394b高速數據傳輸系統。闡述了該系統的硬件設計和軟件工作流程。實驗表明,該系統可靠性高、實時性好、具有廣泛的應用價值。

關鍵詞:IEEE 1394b" title="IEEE 1394b">IEEE 1394b;串行總線;FPGA;Nios II

隨著信息技術的迅速發展,計算機的速度不斷提高,外部設備的速度也隨之提高。常用串行總線,如USB2.0總線最高速率為480 Mb·s-1,IEEE 1394a總線最高速率為400 Mb·s-1,但在有些情況下難以滿足高帶寬和實時性的要求,成為系統性能進一步提升的瓶頸。IEEE 1394 b-2002正是在這種情況下應運而生,它最高支持800 Mb·s-1的總線傳輸速率,最多可支持63個節點,最大傳輸距離100 m,支持即插即用、等時和異步傳輸,并且向下完全兼容IEEE 1394a的設備。1394b串行總線可以應用在眾多的領域中,無論是在視頻傳輸還是計算機外設、網絡互連等方面都有著巨大的市場潛力。具有相同功能的1394b產品,比普通計算機配套設備便宜,具有更好的可擴展性和競爭力。

1 系統的硬件設計及仿真

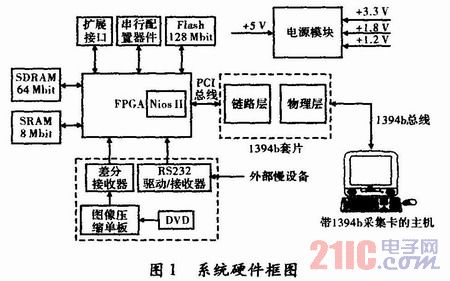

系統硬件設計框圖如圖1所示。根據用戶需求,該系統以FPGA為單板控制核心,外部慢設備的控制或狀態信號通過RS-232總線發送到FP-GA內部的相應接收模塊。這些慢設備發送的數據信息量不大,但要求準確無誤的傳送到主機端顯示,所以這些數據在1394b總線上采用了異步傳輸的方式。除慢設備外,系統單板還通過RS-422差分接收器接收兩路壓縮后的DVD視頻圖像數據。這些圖像數據通過等時傳輸的方式不間斷的發送到主機上,經過解壓縮進行實時播放。系統單板上還留有一些擴展接口,用于功能擴展。

綜合考慮系統的功能需求及實現的復雜度,FPGA采用了Altera公司Cyclone II系列的EP2C70F67216。這款FPGA具有68 416個邏輯單元,422個用戶I/O管腳,I/O標準支持3.3 V PCI,可以通過IP核實現主從模式的PCI接口。在系統中FPGA主要完成:(1)異步與等時數據的接收。(2)數據拼接與數據緩存。(3)外部SRAM的控制,實現大量數據的片外緩存。(4)與鏈路層控制器間的PCI接口時序控制。(5)與Nios II軟核之間的接口模塊。

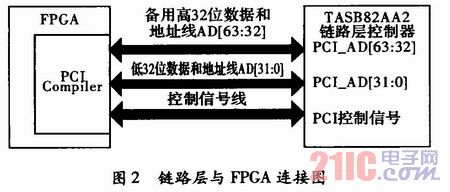

鏈路層控制器TSB82AA2通過PCI總線與FPGA相連,PCI接口的時序較復雜,本設計采用了FPGA內部的IP核PCI_Compiler來實現PCI主從傳輸模式。鏈路層控制器與FPGA的連接關系如圖2所示。在SOPC Builder開發環境中,只需要設置相應的參數,就可以實現PCI總線與FPGA內部Av-alon總線之間的數據交換。需要注意的是,在生成硬件網表前需要加入IP核有關文件中提供的PCI約束信息,并按照約束文件的要求鎖定管腳。

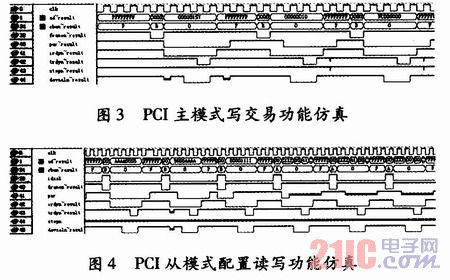

當FPGA為PCI主設備時,它通過PCI-Avalon橋發起PCI主傳輸,如圖3所示是PCI主模式寫交易的仿真時序。當FPGA為PCI從設備時,鏈路層控制器是PCI命令的發起者,并由PCI-Avalon橋自動進行分析,將PCI總線上的命令轉化為相應的Avalon總線信息,圖4所示是PCI從模式配置讀寫仿真圖。

2 嵌入式軟核Nios ll的設計

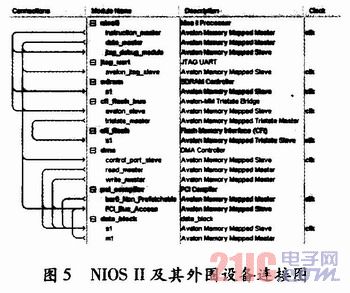

Nios II是Ahera推出的32位RSIC嵌入式處理器,根據用戶的需求有Nios II/f(快速)、Nios II/s(標準)以及Nios II/e(經濟)3種可配置的方案。Nios II還支持片內調試和指令定制,具有較大的靈活性和可擴展性,而且許多常用的標準外設接口已經以IP核的形式集成在了SOPC Builder開發環境中,用戶如需要則可直接調用,縮短了開發周期和成本。根據應用需要,本系統將Nios II配置成快速型,時鐘頻率為100 MHz。Nios II與各種外設通過Avalon總線連接,具體的連接關系如圖5所示。

本系統中Nios II主要完成3個功能:(1)實現1394b設備的自舉,協助主機完成設備識別以及設備的身份確認。(2)實現異步數據收發功能,異步讀、異步寫,根據請求包的類型進行分別處理。(3)滿足傳輸條件時,為等時傳輸申請等時信道和帶寬,成功后開始組織等時傳輸,傳輸結束后釋放信道和帶寬。圖6為Nios II工作流程圖。

下面介紹等時傳輸過程,根據系統設計,將外部DVD壓縮圖像數據作為等時數據來處理。具體過程如下:

(1)NioslI CPU對1394b的OHCI和鏈路層寄存器進行初始化,判斷線纜是否插入,強制根節點,直到設備完成自舉,節點的身份確認,如圖7所示。

(2)自舉過程結束后,Nios II CPU檢測等時傳輸的條件是否滿足,如果滿足則向主機發出申請,申請等時信道和帶寬。

(3)申請成功后,Nios II CPU開始組織數據進行傳輸。首先它向DMA控制器發送寄存器配置信息,從而將數據傳送任務交由DMA控制器完成。

(4)DMA控制器從FPGA的緩存單元中取出數據,并添加包頭將數據拼接成合法的等時數據包格式,并發起PCI主模式傳輸。

(5)數據經由PCI總線傳送到鏈路層芯片中,又通過物理層芯片傳送到1394b總線上,并由主機上連接的數據采集卡接收,最終由主機端的應用程序解壓縮和播放數據。

3 結束語

文中介紹了一種基于FPGA的IEEE 1394b高速數據傳輸系統,它能實現外部多路數據的實時傳送。由于支持1394b的設備與支持1394a的設備可以相互兼容,所以在此基礎上可以建立1394組網平臺,實現多個系統的互聯與傳輸。