1 引 言

UART(Universal Asynchronous Receiver/Transmitter,通用異步收發器)是用于控制CPU與串行設備通信的芯片,將由CPU傳送過來的并行數據轉換為輸出的串行數據流。將系統外部來的串行數據轉換為字節,供系統內部使用并行數據的器件使用。他可以在輸出的串行數據流中加人奇偶校驗位和啟停標記,并對從外部接收的數據流進行奇偶校驗以及刪除啟停標記。常見UART主要有INS8250,PC16450和PCI6550,其中16550發送和接收都帶有16 B的FIFO,為協調發送、接收端的速率匹配提供了更大的緩沖余地,同時也可以提高CPU的使用效率,從而提高系統的整體性能。

2 UART16550的基本結構

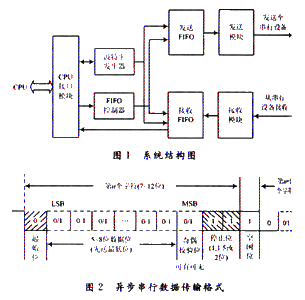

如圖1所示,UART16550的基本結構由CPU接口模塊、波特率發生器、FIFO控制器、發送/接收FIFO和發送/接收模塊共7個部分組成。

CPU通過UART的CPU接口模塊配置整個UART,波特率發生器在CPU寫入初始值后產生需要的波特率,控制發送和接收模塊在設定的波特率下工作。CPU通過接口模塊向發送FIFO內寫入

需

要發送的8位數據,同時發送模塊開始讀取FIFO中的數據,并加入起始位、奇偶校驗位和停止位后以串行發送的方式傳輸給串行接收設備。接收模塊時刻監視串行輸入端口,發現有數據發送來的時候馬上啟動接收模塊開始接收數據并有效的判斷出奇偶校驗位來檢測數據的正確性,最后把剩下的8位數據放入接收FIFO,并通知CPU有數據進來進行接收。異步串行通信協議的數據傳輸格式如圖2所示。

UART16550的發送數據位可以選擇為5~8位,同時可以選擇奇校驗、偶校驗或者不設置校驗位,停止位可以約定為1,1.5或2位。

3 UART16550的設計實現

3.1 CPU接口模塊

CPU接口模塊完成了CPU指令的解讀與寄存器配置以及UART狀態讀取等功能。通過3位的地址線和8位的數據線,CPU可以對波特率發生器的波特率進行預先的設定,以使串口兩端的設備在同一波特率下完成接收和發送的工作。同時CPU接口接收來自CPU的需要發送的5∽8位數據,送人發送模塊,或者把接收模塊接收到的數據通過接口送給CPU進行數據處理。在此接口模塊里,設置了8個控制和狀態寄存器,包括RBR(Receiver Buffer Register)接收緩沖寄存器、THR(Transmit Hold Register)發送保持寄存器、IER(Interrupt Enable Register)中斷使能寄存器、IIR(Interrupt ID Register)中斷寄存器、LCR(Line Control Register)線控制寄存器、LSR(Line Status Register)線狀態寄存器、SCR(Scratchpad Register)暫存寄存器和FCR(FIFO Control Register)。在使用UART16550前,CPU必須要對控制寄存器進行配置,包括波特率、數據位數、奇偶校驗、停止位位數及FIFO的控制等。這也是16550區別于一般UART的具有可編程的特點。

3.2波特率發生器

波特率是單位時間內傳送的二進制數據的位數,以位/秒(b/s)表示,也稱為數據位率。

收/發時鐘頻率與波特率之間關系:

收/發時鐘頻率=N×波特率

N可以取8,16,32和64等,為了兼顧速度和穩定性一般取為16。N在硬件設計時已經設定好,軟件不能改變。波特率發生器由兩個8位的數據寄存器組合成16位的分頻寄存器,可以實現系統頻率的1~2(16)分頻,達到預定的波特率設置。

3.3 FIFO控制器和發送/接收FIFO

帶有緩存是16550以及更高端UART的突出的特點。16550帶有8位寬、16字節深的異步FIFO。FIFO控制器從CPU接口讀入信息,配置發送/接收FIFO,并且在需要的時候使能FIFO,并且把FIFO的實時狀態通過CPU接口送給CPU以方便CPU讀取數據。在發送FIFO空和接收FIFO滿的時候,FIFO控制器立即產生中斷請求,通知CPU進行下一步的操作。另外,當配置DMA模式時,CPU可以進行大數據量的發送和讀取,減輕了CPU的負擔,可以提高整個系統的運行效率。

3.4發送模塊

發送模塊的核心是one hot編碼的狀態機。他可以讀人來自FIFO的數據,并根據配置寄存器里面的信息加入起始位、1,1.5或2位停止位和奇偶校驗位,然后把打包的數據通過移位寄存器把數據以標準的串口協議發送給串口接收設備。只要發送FIFO中有數據存在,發送模塊就會一直發送,直到FIFO空為止。在不選擇FIFO的情況下,發送模塊則直接接收來自THR(Transmit Hold Register)發送保持寄存器的數據,不經過緩存直接發送。

3.5接收模塊

接收模塊是發送模塊功能的逆序執行。他接收來自外部的串行數據,根據配置去除數據的起始、停止位和奇偶校驗位,若出現數據差錯則立即產生錯誤信息。如果沒有錯誤,則將剩余的8位有用數據送入接收FIFO讓CPU讀取。同樣接收模塊也可以選擇不使用FIFO,這時接收模塊就會把8位數據直接送給RBR(Receive Buffer Register)接收緩沖寄存器,再由RBR送給CPU。

4結果的驗證仿真

設計采用VHDL語言在FPGA Advantage平臺下編寫,并通過Modelsim編譯仿真,并且通過ISE下載到電路板上驗證,硬件驗證FPGA芯片采用Xilinx的Spartan3。XC400PQ208。由于驗證UART接收/發送時序必須要有處理器,所以采用在FPGA內部嵌入Xilinx的MicroBlaze軟核模擬CPU控制時序,通過FPGA外接的串口實現與計算機串口進行通信。

5 結 語

本文介紹了UARTl6550在可編程邏輯器件FPGA上的實現,并通過實際電路驗證了設計的功能,使用FP-GA不僅可以方便地用串口協議與PC機進行串行通信,而且擴展了板級系統的接口功能。應用在可編程器件FPGA內部,可以很大程度地減少電路板的使用面積,并提高系統的穩定性和可編程性。